# Reducing Memory Usage by the Lifting-based Discrete Wavelet Transform with a Unified Buffer on a GPU

Takuya Ikuzawa<sup>a,b</sup>, Fumihiko Ino<sup>a,\*</sup>, Kenichi Hagihara<sup>a</sup>

<sup>a</sup>Graduate School of Information Science and Technology, Osaka University, 1-5 Yamada-oka, Suita, Osaka 565-0871, Japan

<sup>b</sup>Industrial ICT Solutions Company, Toshiba Corporation, 72-34 Horikawa-cho, Saiwai-ku, Kawasaki, Kanagawa 212-0013, Japan

# Abstract

In this study, to improve the speed of the lifting-based discrete wavelet transform (DWT) for large-scale data, we propose a parallel method that achieves low memory usage and highly efficient memory access on a graphics processing unit (GPU). The proposed method reduces the memory usage by unifying the input buffer and output buffer but at the cost of a working memory region that is smaller than the data size n. The method partitions the input data into small chunks, which are then rearranged into groups so different groups of chunks can be processed in parallel. This data rearrangement scheme classifies chunks in terms of data dependency but it also facilitates transformation via simultaneous access to contiguous memory regions, which can be handled efficiently by the GPU. In addition, this data rearrangement is interpreted as a product of circular permutations such that a sequence of seeds, which is an order of magnitude shorter than input data, allows the GPU threads to compute the complicated memory indexes needed for

Preprint submitted to Journal of Parallel and Distributed Computing

<sup>\*</sup>Corresponding author. Tel.: +81 6 6879 4353; fax: +81 6 6879 4354. *Email address:* ino@ist.osaka-u.ac.jp(Fumihiko Ino)

parallel rearrangement. Because the DWT is usually part of a processing pipeline in an application, we believe that the proposed method is useful for retaining the amount of memory for use by other pipeline stages. *Keywords:* Discrete wavelet transform, lifting scheme, memory-saving

computation, in-place algorithm, GPU

# 1. Introduction

The discrete wavelet transform (DWT) [1] is a well-known method for timefrequency analysis, which analyzes a signal in both the time and frequency domains using various time-frequency representations. The DWT employs wavelets as these representations, or scaled and translated versions of a finite-length or fastdecaying oscillating waveform called a mother wavelet. The DWT is useful for classifying the input signal into high-frequency components and low-frequency components in the same manner as the traditional fast Fourier transform (FFT). Given a signal with n samples (we assume that n is a power of 2), the DWT can be processed within  $\mathcal{O}(n)$  time, whereas the FFT requires  $\mathcal{O}(n \log n)$  time; consequently, the DWT is more computationally efficient than the FFT. Similar to the FFT, the DWT is a separable filter. For example, a two-dimensional (2-D) DWT filter can be realized by row-wise and column-wise (horizontal and vertical) 1-D DWT filters. The DWT is useful in various fields, such as data compression for images [2, 3, 4], artifact removal [5], data decoding for earth observation satellites [6] and clustering analysis for geometrical data [7]. These typical applications usually employ multiresolution analysis [1], where the DWT is applied recursively to low-frequency components at each resolution level of the hierarchy. Therefore, a fast DWT implementation is required to process DWT-based applications in real-time.

Acceleration methods for the DWT can be classified into two types: algorithmbased and accelerator-based approaches. An example of the former is the lifting scheme [8], which halves the computational requirements of the traditional filter bank scheme [9]. Furthermore, the lifting scheme is an in-place algorithm, which is capable of overwriting the algorithm's output onto the input buffer; thus, the lifting scheme reduces the amount of memory usage by half compared with the filter bank scheme. In this study, an in-place algorithm is defined as an algorithm that requires  $\mathcal{O}(1)$  memory space, excluding the input buffer of size n.

The DWT has also been implemented in many accelerators, such as graphics processing units (GPUs) [10], field programmable gate arrays [11], and cell broadband engines [12, 13]. The GPU is one of the most popular commodity devices among these hardware types, where it provides a much higher memory bandwidth than the CPU. For example, the latest Maxwell architecture [14] provides 336 GB/s of memory bandwidth, which is one magnitude higher than that of the double data rate fourth generation (DDR4) memory. Consequently, many memory-bound applications have been successfully accelerated on GPUs [15, 16, 17]. The DWT is a memory-bound operation rather than a compute-bound operation, so we consider that the GPU is a promising accelerator for the DWT.

Laan *et al.* [10] accelerated the lifting scheme on a GPU that is compatible with the compute unified device architecture (CUDA) [18]. They implemented

row-wise and column-wise 1-D DWTs as kernel functions, which are then offloaded from the CPU to the GPU. Their kernels facilitate efficient memory access by using a data layout that stores high-frequency components in a contiguous memory region. After the high-frequency components, low-frequency components are also stored in a contiguous memory region. This data layout is useful for maximizing the effective memory bandwidth on a GPU because memory transactions are performed per warp, i.e., a series of GPU threads that executes the same instruction every clock cycle [18], where the threads in a warp are allowed to access a contiguous memory region simultaneously via a 128-byte memory transaction.

However, this layout distinguishes the output buffer from the input buffer, thereby eliminating the advantage of in-place transformation. For signal data larger than half of the GPU memory capacity, the data must be swapped from the GPU memory to the CPU memory. This data transfer between the CPU and GPU degrades the overall transformation performance because the peak bandwidth of the PCI Express (PCIe) bus is 15.8 GB/s, which is one magnitude lower than that of the GPU memory. In addition, the DWT is usually part of a processing pipeline in an application, so it is better to retain the amount of memory for use by other pipeline stages.

In this study, in order to obtain a fast lifting-based DWT for large-scale data, we propose a parallel method that reduces the amount of memory usage and that facilitates highly efficient memory access on a CUDA-compatible GPU. The proposed method achieves memory-saving transformation by unifying the input buffer and the output buffer but with the cost of a tiny working memory space, which is less than the input size n. Naive unification avoids parallelizing the lifting scheme because the unified buffer causes many flow dependencies during transformation. To address this issue, the proposed method partitions the input data into small chunks, which are then rearranged in an appropriate manner so the parallel DWT can be performed over the unified buffer. Thus, this data rearrangement can be regarded as a preprocessing phase that classifies the input data into groups so different groups are independent of each other, where data-dependent tasks within the same group are processed sequentially, but different groups can be processed in parallel. Furthermore, chunk operations can be processed in a single-instruction, multiple-data (SIMD) manner because each chunk comprises multiple data elements.

In addition to the buffer unification mentioned above, the proposed method performs the DWT via simultaneous access to contiguous regions. Thus, after the chunks have been generated using this GPU-friendly access pattern, the generated chunks can also be placed in appropriate positions by this favorable access pattern. Allowing the GPU threads to compute the complicated memory addresses where their responsible chunks must be placed is a challenging issue. In particular, irregular addresses must be computed from very small amounts of information with a data size less than n to maintain the advantage of the in-place transformation. To tackle this issue, the proposed method represents a sequence of memory addresses as a circular permutation. This interpretation allows us to precompute a small sequence of numbers, which can then be used as seeds to produce the sequence of

memory addresses for use in data rearrangement.

The remainder of this paper is organized as follows. Section 2 introduces related research on GPU-accelerated DWT implementations. Section 3 summarizes the lifting scheme, which forms the basis of the proposed method. Section 4 describes the proposed method and Section 5 presents the experimental results. Finally, Section 6 gives the conclusions.

# 2. Related Work

Table 1 compares related research into the acceleration of the DWT on GPUs. Each study employed different hardware so the peak performance is presented with the transformation throughput to allow standardization. To the best of our knowledge, no previous GPU-based implementation has achieved a compact data representation and data arrangement that enables GPU-friendly memory accesses for the lifting-based DWT.

Wong *et al.* [19] implemented the filter bank scheme on a GeForce 7800 GTX GPU, where their five-level DWT implementation was based on OpenGL [20], or a graphics application programming interface (API). They selected the filter bank scheme rather than the lifting scheme because the data dependencies in the lifting scheme are more complex than those in the filter bank scheme. These complex data dependencies cannot be handled efficiently by OpenGL, which is specialized for graphics applications, because OpenGL has many restrictions on its programming capability compared with CUDA. For example, OpenGL prohibits the explicit management of an on-chip cache called *shared memory* [18]. Despite these

restrictions, Tenllado *et al.* [21] implemented the lifting scheme using OpenGL. However, they found that the filter bank scheme was faster than the lifting scheme due to the complex data dependencies mentioned above.

Franco *et al.* [22] implemented the filter bank scheme on a Tesla C870 GPU. They adopted a row-column approach, which reuses a horizontal DWT kernel as a vertical DWT kernel by transposition. Their implementation transformed an  $8192 \times 8192$ -pixel image within 71 ms and the transformation throughput reached 0.9 Gpixel/s. However, the overall performance was limited by data transfer between the CPU and GPU. Transferring the data between the CPU and GPU required 163 ms, so the transformation throughput dropped to 0.3 Gpixel/s after considering these overheads. A similar row-column approach was presented by Galiano *et al.* [23].

To the best of our knowledge, Matela *et al.* [3] first implemented the filter bank scheme on a CUDA-compatible GPU. Their implementation was based on a block-based approach, which allows the horizontal and vertical DWT kernels to be merged into a single kernel. Their implementation copies 2-D blocks into the shared memory, which can be commonly accessed from threads in the same thread block [18]. This on-chip memory is useful for saving the GPU memory bandwidth, so that the ratio R of the memory throughput over the peak memory bandwidth was more than 1.0. That is, on-chip data was efficiently shared among threads. In their implementation, they distinguished the output region from the input region.

Laan et al. [10] proposed a hybrid of the row-column and block-based ap-

proaches. Their horizontal process is same as that in the row-column approach. By contrast, their vertical process avoids transposition by applying the vertical DWT to vertically-long blocks. Furthermore, a sliding window mechanism was developed to reuse on-cache data fetched from the GPU memory. Similar to the block-based approach [3], this hybrid approach increased the ratio R to more than 1.0. Using a GeForce 8800 GTX card, their implementation achieved a transformation throughput of 1.5 Gpixel/s for a  $4096 \times 4096$ -pixel image. This throughput was roughly  $\times 3$  higher than those achieved by a row-column scheme and an OpenGL-based implementation [21]. As presented theoretically in [8], Laan et al. demonstrated that the lifting scheme was two times faster than the filter bank scheme on the CUDA-compatible GPU. Kucis et al. [24] presented an extension of Laan's method that reduces synchronization by allowing redundant computation between threads. This extended method achieved a transformation throughput of 8.3 Gpixel/s on a GeForce GTX 580 card, which was 30% faster than the basic method. However, after considering the data transfer between the CPU and GPU, the transformation throughput decreased to 0.4 Gpixel/s.

Sharma *et al.* [25] used OpenCL [26] to implement the lifting scheme on a GeForce GTX 285 GPU. OpenCL is a standard for heterogeneous computing platforms, so their implementation ran on CUDA-incompatible GPUs and multicore CPUs. Their OpenCL-based implementation achieved a transformation throughput of 0.4 Gpixel/s for a  $4096 \times 4096$ -pixel image, but it was slower than that of their CUDA-based implementation, which was 0.7 Gpixel/s.

Table 1: Comparison of related research. P denotes the peak memory bandwidth for the GPU employed.  $\rho$  and  $\rho^+$  denote the transformation throughputs without and with data transfer time between the CPU and GPU, respectively. For the *L*-level DWT, the number  $\mathcal{N}$  of transformed pixels is given by  $\mathcal{N} = \sum_{k=1}^{L} N^2/4^{k-1}$  because the level k transforms an  $N/2^{k-1} \times N/2^{k-1}$ -pixel region.  $R = \mathcal{N}A/T/P$  is the ratio of the memory throughput over the peak memory bandwidth P, where A and T are the amount of memory access per pixel and the execution time, respectively. The proposed method assumes that a chunk comprises b = 512 elements.

|                 |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01 <b>2</b> 010111011001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                                                        |                                                        |                                                        |                                                        |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| DWT scheme      | API                                                                                                                                                                      | GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Memory                                                 | P                                                      | R                                                      | Throughp                                               | out (Gpixel/s)                                         |

| (level)         |                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | capacity (MB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (pixel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | usage                                                  | (GB/s)                                                 |                                                        | ρ                                                      | $\rho^+$                                               |

| Filter bank (5) | OpenGL                                                                                                                                                                   | 7800 GTX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2K \times 2K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 38                                                     | _                                                      | _                                                      | 0.003                                                  |

| Lifting (5)     | OpenGL                                                                                                                                                                   | 7800 GTX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2K \times 2K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 38                                                     | 0.33-0.73                                              | 0.3-0.4                                                | _                                                      |

| Filter bank (5) | OpenGL                                                                                                                                                                   | 7800 GTX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2K \times 2K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 38                                                     | 0.57-0.66                                              | 0.3-0.6                                                | _                                                      |

| Filter bank (1) | CUDA                                                                                                                                                                     | Tesla C870                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1536                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8K×8K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2n                                                     | 77                                                     | 0.49                                                   | 0.9                                                    | 0.3                                                    |

| Lifting (3)     | CUDA                                                                                                                                                                     | 8800 GTX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $4K \times 4K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 86                                                     | 1.22                                                   | 1.5                                                    | _                                                      |

| Lifting (1)     | CUDA                                                                                                                                                                     | GTX 295                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $2K \times 2K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 112                                                    | 1.67                                                   | 2.6                                                    |                                                        |

| Lifting (1)     | CUDA                                                                                                                                                                     | GTX 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $4K \times 4K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 142                                                    | 0.97                                                   | 2.5                                                    |                                                        |

| Lifting (3)     | OpenCL                                                                                                                                                                   | GTX 285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $4K \times 4K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 159                                                    | 0.11                                                   | 0.4                                                    |                                                        |

| Lifting (3)     | CUDA                                                                                                                                                                     | GTX 285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $4K \times 4K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 159                                                    | 0.18                                                   | 0.7                                                    | _                                                      |

| Lifting (1)     | CUDA                                                                                                                                                                     | GTX 580                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1536                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $4K \times 4K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2n                                                     | 192                                                    | 3.11                                                   | 8.3                                                    | 0.4                                                    |

| Lifting (1)     | CUDA                                                                                                                                                                     | GTX 580                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1536                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16K×16K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $n + \lceil n/2b \rceil$                               | 192                                                    | 1.27                                                   | 2.8                                                    | 0.7                                                    |

| Lifting (1)     | CUDA                                                                                                                                                                     | GTX 980 Ti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $32K \times 32K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $n + \lceil n/2b \rceil$                               | 336                                                    | 1.38                                                   | 5.3                                                    | 2.0                                                    |

|                 | DWT scheme<br>(level)<br>Filter bank (5)<br>Lifting (5)<br>Filter bank (5)<br>Filter bank (1)<br>Lifting (3)<br>Lifting (1)<br>Lifting (3)<br>Lifting (1)<br>Lifting (1) | DWT scheme         API           (level)            Filter bank (5)         OpenGL           Filter bank (5)         OpenGL           Filter bank (5)         OpenGL           Filter bank (1)         CUDA           Lifting (3)         CUDA           Lifting (1)         CUDA           Lifting (3)         OpenCLL           Lifting (3)         OpenCLL           Lifting (3)         CUDA           Lifting (3)         CUDA           Lifting (3)         CUDA           Lifting (1)         CUDA | DWT scheme         API         GPU           (level)         Filter bank (5)         OpenGL         7800 GTX           Filter bank (1)         CUDA         Tesla C870           Lifting (3)         CUDA         8800 GTX           Lifting (1)         CUDA         GTX 285           Lifting (3)         OpenCL         GTX 285           Lifting (3)         CUDA         GTX 285           Lifting (1)         CUDA         GTX 580           Lifting (1)         CUDA         GTX 580           Lifting (1)         CUDA         GTX 580 | DWT scheme         API         GPU         Memory<br>capacity (MB)           Filter bank (5)         OpenGL         7800 GTX         512           Lifting (5)         OpenGL         7800 GTX         512           Filter bank (5)         OpenGL         7800 GTX         512           Filter bank (5)         OpenGL         7800 GTX         512           Filter bank (1)         CUDA         Tesla C870         1536           Lifting (3)         CUDA         GTX 295         896           Lifting (1)         CUDA         GTX 280         1024           Lifting (3)         OpenCL         GTX 285         1024           Lifting (3)         CUDA         GTX 285         1024           Lifting (3)         CUDA         GTX 285         1024           Lifting (1)         CUDA         GTX 580         1536           Lifting (1)         CUDA         GTX 580         1536 | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

#### 3. Lifting based DWT

Let  $x_0, x_1, \ldots, x_{n-1}$  be the input signal with n samples. We assume that n is a power of two. Given the input signal, the DWT outputs its low-frequency components  $c_0, c_1, \ldots, c_{n/2-1}$  and high-frequency components  $d_0, d_1, \ldots, d_{n/2-1}$ . In the lifting scheme [8], the *t*-th element  $c_t$  of low-frequency components and  $d_t$  of high-frequency components, where  $0 \le t < n/2$ , are given by

$$c_t = x_{2t} + \sum_{i=-k_0}^{k_0 - 1} u_i d_t, \tag{1}$$

$$d_t = x_{2t+1} - \sum_{j=-k_1+1}^{k_1} p_j x_{2(t+j)}, \qquad (2)$$

where  $u_i$   $(-k_0 \le i < k_0)$  and  $p_j$   $(-k_1 < j \le k_1)$  are coefficients determined by the mother wavelet. The data dependencies in Eqs. (1) and (2) indicate that in-place transformation can be achieved by overwriting  $d_t$  to  $x_{2t+1}$ , then  $c_t$  to  $x_{2t}$ . This access pattern implies a cyclic layout, which stores the low-frequency element  $c_t$  and highfrequency element  $d_t$  alternately:  $c_0, d_0, c_1, d_1, \ldots, c_{n/2-1}, d_{n/2-1}$ . Using this layout, the DWT can be implemented with two kernels, a high-pass filter kernel for computing high-frequency components and a low-pass filter kernel for computing low-frequency components.

One drawback of the cyclic layout is that it requires data packing to obtain the filtered result, where the high- and low-frequency components are stored in odd and even elements, respectively (note that the indexes start from zero). Furthermore, the cyclic layout cannot maximize the memory throughput during transformation because both kernel functions cause a memory stride of two, where the high- and low-pass kernels output odd and even elements, respectively. As a further issue, the memory stride doubles at every hierarchical level of the multiresolution analysis, where the DWT is applied recursively to low-frequency components.

#### 3.1. Laan's Previous Method

Laan *et al.* [10] presented a solution to the data layout issue. Their method increases the efficiency of memory access by using a block layout, which stores lowfrequency components and high-frequency components in contiguous regions:  $c_0, c_1, \ldots, c_{n/2-1}, d_0, d_1, \ldots, d_{n/2-1}$ . However, this method separates the output buffer from the input buffer due to the data dependencies inherent in Eqs. (1) and (2). Consequently, it eliminates the advantage of in-place transformation and consumes double the memory space, as mentioned in Section 1.

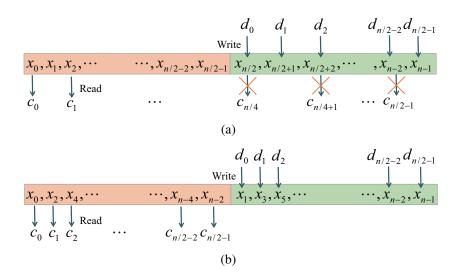

Consider here a block layout that naively unifies the input buffer and the output buffer. As shown in Fig. 1(a), the high-pass filter kernel outputs high-frequency element  $d_t$  to  $x_{t+n/2}$ , where  $0 \le t < n/2$ . However, this execution eliminates part of the original elements,  $x_{n/2}, x_{n/2+2}, \ldots, x_{n-2}$ , which are needed by the second kernel to compute  $c_{n/4}, c_{n/4+1}, \ldots, c_{n/2-1}$ , as indicated in Eq. (1).

Two alternative approaches can be employed to avoid this elimination: a serialization approach that sequentially processes data-dependent tasks or a duplication approach that copies all of the elements,  $x_0, x_1, \ldots, x_{n-1}$ , to another memory region before outputting the computational results. The former approach fails to take advantage of massively parallel computing on the GPU. The latter approach corresponds to the previous method [10], which separates the output buffer from the input buffer.

# 4. Proposed Method

Similar to Laan's previous method [10], the proposed method employs a block layout to exploit the high peak memory bandwidth of the GPU. Furthermore, the proposed method rearranges the data elements so the odd elements follow the even elements, as shown in Fig. 1(b). This rearrangement is performed on a per-chunk basis, where each chunk contains b elements. Next, the method computes Eqs. (1) and (2) to complete the lifting operation [10]. For simplicity, we assume 1-D data in the following discussion.

Figure 1: Memory access pattern in lifting-based DWT. (a) When writing high-frequency components, a naive unification scheme eliminates the original elements needed for the latter half of the low-frequency components. (b) By contrast, the proposed scheme maintains the original elements after writing the high-frequency components.

## 4.1. Data Rearrangement

The proposed method rearranges the input data according to the following two steps.

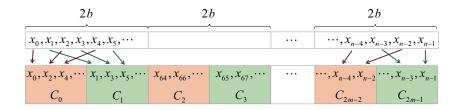

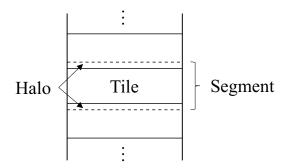

Chunk generation: Given an input signal x<sub>0</sub>, x<sub>1</sub>,..., x<sub>n-1</sub> with n samples, the method constructs an even chunk and an odd chunk within every segment of 2b elements (see Fig. 2). An even chunk contains even elements whereas an odd chunk contains odd elements. In the following discussion, let m (= [n/2b]) be the number of even chunks. For simplicity, the number of odd chunks is assumed to be the same as that of even chunks; thus, the total number of chunks is given by 2m. To facilitate highly efficient memory access, the chunk size is assumed to be a multiple of 128 bytes be-

Figure 2: Chunk generation. Even and odd chunks are generated within every segment of 2b elements. After generation, even and odd chunks appear alternately.

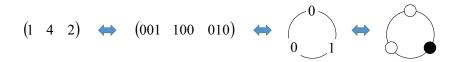

Figure 3: Chunk rearrangement (m = 4). Odd chunks follow even chunks after rearrangement. Note that  $C_0$  is an even chunk because the indexes start from zero.

cause the current CUDA accesses the global memory via 128-byte memory transactions [18].

Chunk rearrangement: 2m chunks are rearranged such that m odd-chunks appear after m even-chunks, as shown in Fig. 3. More formally, the 2i-th chunk and the (2i + 1)-th chunk, where 0 ≤ i < m, are placed in the i-th chunk and the (i + m)-th chunk after rearrangement.</li>

Algorithm 1 shows the proposed chunk generation algorithm, which describes the kernel function that needs to be executed by massive GPU threads in parallel. This algorithm assumes that a thread block [18] containing 2b threads is responsible for generating two chunks within a segment of 2b elements. Each thread loads its responsible element from the global memory to a shared array s of size  $3 \times b$  (line 3), before performing local synchronization within the thread block. Note that the last column of this array is a dummy region padded for avoiding bank conflicts [18] when writing the loaded element back to the appropriate location in the global memory (line 10). This row-wise algorithm can easily be extended to a column-wise algorithm without using the shared memory. As described in [10], column-wise operations can be achieved by assigning a row of 32 neighboring columns to a warp, where every warp is allowed to access a contiguous memory region.

Algorithm 1 Chunk generation kernel.

| <b>Input:</b> Input signal $x_0, x_1, \ldots, x_{n-1}$ with n samples and b elements in a chun | K   |

|------------------------------------------------------------------------------------------------|-----|

| <b>Output:</b> Per-chunk rearranged elements $x_0, x_2, \ldots, x_{n-1}$ containing altern     | ate |

| odd and even chunks                                                                            |     |

- 1:  $i \leftarrow$  thread index; 2:  $j \leftarrow$  thread block index;

- > Load responsible element into a shared array of size 3:  $s_{i\%2,|i/2|} \leftarrow x_{2bj+i};$  $3 \times b$

- 4: \_\_synchthreads(); Local synchronization ▷ Even chunk generation 5: **if** *i* < *b* **then**  $k \leftarrow 2i;$ 6:

- ▷ Odd chunk generation

$k \leftarrow 2(i-b) + 1;$ 9: **end if**

7: **else**

8:

10:  $x_{2bj+i} \leftarrow s_{k\%2,|k/2|};$

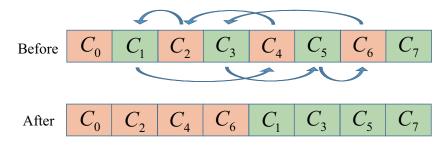

Chunk rearrangement can be represented as a product of *l* circular permutations:  $\sigma_0 \circ \sigma_1 \circ \ldots \circ \sigma_{l-1}$ , where  $\sigma_j \ (0 \le j < l)$  represents the j-th circular permutation. Let (i j) be a transposition representing an exchange between the *i*-th chunk and the *j*-th junk. The chunk rearrangement for m = 4 shown in Fig. 3 can then be formulated as a product of two circular permutations,  $(1 \ 4 \ 2) \circ (3 \ 5 \ 6)$ . According to this interpretation, a circular permutation  $(1 \ 4 \ 2)$  represents a datadependent task that circulates chunks  $C_1$ ,  $C_4$  and  $C_2$ . Thus, a task is a series of chunk movements that must be processed sequentially. However, different circular permutations are independent of each other, so they can be processed in parallel. Therefore, the proposed method assigns a circular permutation to a thread block, which then sequentially processes a series of chunk movements that corresponds to the assigned circular permutation. Note that a chunk contains multiple data elements; thus, the data elements within a chunk can be processed simultaneously by *b* threads from the same thread block in a SIMT manner.

A critical issue is how to formulate circular permutations according to the number n of samples. To address this issue, we introduce the following lemma.

**Lemma 1.** Let *s* be the size of an arbitrary circular permutation  $\sigma_j$   $(0 \le j < l)$ , which represents a series of chunk movements in step 2. Then,  $s \le \lceil \log 2m \rceil$ .

**Proof**. Let  $(a_0 \ a_1 \ a_2 \ \dots \ a_{s-1})$  be an arbitrary circular permutation, which represents a series of chunk movements in step 2, where this permutation indicates that chunks  $C_{a_0}, C_{a_1}, \dots, C_{a_{s-1}}$  must be circulated. Then, for all  $0 \le k < s$ ,  $0 \le a_k < 2m$  because there are 2m chunks in total. According to step 2, we have Eq. (3).

$$a_{k} = \begin{cases} a_{k+1}/2, & \text{if } a_{k+1} \text{ is even,} \\ \lfloor a_{k+1}/2 \rfloor + m, & \text{otherwise.} \end{cases}$$

(3)

Note that for all  $0 \le k < s$ ,  $a_k$  can be represented as a binary number with  $\lceil \log 2m \rceil$  bits. In this binary representation, applying a circular right shift to  $a_{k+1}$  gives  $a_k$ , as indicated by Eq. (3). For example, the permutation  $(1 \ 4 \ 2)$  has three elements, 1, 4, and 2, which correspond to binary representations of 001, 100, and 010, respectively, and the last two elements can be obtained by applying a circular right shift to the first element 001 (see Fig. 4). Therefore, for an arbitrary  $a_k$ , applying a circular right shift at most  $\lceil \log 2m \rceil$  times to  $a_k$  produces itself; thus,  $s \le \lceil \log 2m \rceil$ .

Figure 4: Interpretation of chunk rearrangement with a circular permutation. A circular permutation of length M can be mapped to a necklace with M beads and two colors, where rotations are considered equivalent. In this example, M = 3.

According to Eq. (3), we have Eq. (4):

$$a_{k+1} = 2a_k \bmod (2m-1), \tag{4}$$

where  $0 \le k < s$ . Thus, the representative element  $a_0$  of a circular permutation produces all the elements of that circular permutation. This means that the final memory location for an arbitrary chunk can be computed from  $a_0$ , i.e., a seed.

Algorithm 2 describes the proposed method for rearranging chunks according to step 2. This algorithm assumes that the process uses l thread blocks of size b and three inputs: (1) 2m chunks that need to be rearranged, (2) the number l of circular permutations, and (3) their representative elements  $p_0, p_1, \ldots, p_{l-1}$ , where  $p_j$  is the representative element for circular permutation  $\sigma_j$  ( $0 \le j < l$ ). Given these inputs, the thread block with index j loads a chunk that corresponds to the representative element  $p_j$  in a register (line 2). Next, another chunk that corresponds to the next element in circular permutation  $\sigma_j$  is moved into the empty memory location where the copied chunk was present (line 5). Similar chunk movements are iterated until the representative element  $p_j$  from the register into the last empty location (line 8). Note that this rearrangement is optimal in terms of the amount of memory access because all of the chunks that must move to a

different location are loaded once and stored once.

Algorithm 2 Chunk rearrangement kernel based on a product of circular permutations.

**Input:** Chunks  $C_0, C_1, \ldots, C_{2m-1}$  that need to be rearranged, number 2m of chunks, and representative elements  $p_0, p_1, \ldots, p_{l-1}$  of circular permutations **Output:** Rearranged chunks  $C_0, C_1, \ldots, C_{2m-1}$

| 1: $j \leftarrow$ thread block index;   |                                                    |

|-----------------------------------------|----------------------------------------------------|

| 2: $W \leftarrow C_{p_j};$              | $\triangleright b$ elements are copied in parallel |

| 3: $i \leftarrow p_j$ ;                 |                                                    |

| 4: while $2i \mod (2m-1) \neq p_j$ do   |                                                    |

| 5: $C_i \leftarrow C_{2i \mod (2m-1)};$ | $\triangleright b$ elements are copied in parallel |

| 6: $i \leftarrow 2i \mod (2m-1);$       |                                                    |

| 7: end while                            |                                                    |

| 8: $C_i \leftarrow W;$                  | $\triangleright b$ elements are copied in parallel |

#### 4.2. Precomputation of Representative Elements

In order to perform the in-place DWT, the GPU threads must compute the number l of circular permutations and all the representative elements  $p_0, p_1, \ldots, p_{l-1}$ , for an arbitrary problem size n. In particular, the representative elements must be assigned to thread blocks without duplication. However, it is not easy to parallelize this assignment to GPU threads, mainly due to the lack of a global synchronization mechanism.

Our solution to this issue is to precompute the number l of circular permutations and representative elements  $p_0, p_1, \ldots, p_{l-1}$  on the CPU. Algorithm 3 describes our sequential algorithm for computing all the representative elements. This algorithm enumerates all of the elements in a circular permutation  $\sigma_j$  and stores the minimum value as  $p_j$ . The representative elements are computed per circular permutation, so an array X is used to avoid duplicated enumeration.

Algorithm 3 Precomputation of representative elements for circular permutations. **Input:** Number 2m of chunks **Output:** Number *l* of circular permutations and representative elements  $p_0, p_1, \ldots, p_{l-1}$  of circular permutations 1: for  $i \leftarrow 0$  to 2m - 1 do ▷ Initialization  $X_i \leftarrow 0;$ 2: 3: end for 4:  $l \leftarrow 0$ ; 5: for  $i \leftarrow 0$  to 2m - 1 do  $\triangleright$  Compute  $p_l$ if  $X_i = 0$  then ▷ Not registered yet 6: 7:  $p_l \leftarrow i;$  $X_i \leftarrow 1;$ 8: 9:  $j \leftarrow 2i \mod (2m-1)$ ;  $\triangleright$  Generate number j such that j and i belong to the same circular permutation while  $j \neq i$  do 10:  $X_j \leftarrow 1;$ 11:  $j \leftarrow 2j \mod (2m-1);$ 12: end while 13: 14:  $l \leftarrow l + 1;$ end if 15: 16: **end for**

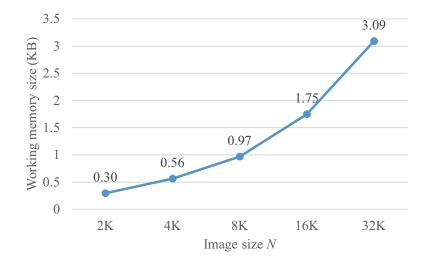

The representative elements  $p_0, p_1, \ldots, p_{l-1}$  are then transferred to constant memory [18] (i.e., GPU memory) before generating chunks on the GPU. Note that the capacity of constant memory is 64 KB in the current CUDA. This capacity is sufficiently large to store representative elements for the largest problem size nthat can be processed on a GPU. A detailed analysis is provided in Section 5.1.

## 4.3. Space Complexity Analysis

The proposed method requires two different working spaces to perform the DWT: (1) constant memory used for representative elements, and (2) shared memory and registers used for chunk generation and circulation.

The constant memory usage depends on the number l of representative elements. The following lemma [27] is introduced to formulate l for arbitrary n.

**Lemma 2.** According to Burnside's lemma [28], the number of necklaces with M beads and K (> 1) colors (see Fig. 4), where rotations are considered to be equivalent, is

$$\frac{1}{M}\sum_{i|M}\mu\left(\frac{M}{i}\right)K^{i} = \frac{1}{M}\sum_{i=1}^{M}K^{\operatorname{gcd}(i,M)},$$

(5)

where  $\mu$  is the classical Möbius function and gcd(i, M) is the greatest common divisor of i and M.

Thus, the number l+2 is equivalent to that of necklaces with  $M = \lceil \log 2m \rceil$  beads and K = 2 colors, where rotations are considered to be equivalent. Note that "+2" considers two exceptions, permutations  $(0 \ 0 \ \dots 0)$  and  $(1 \ 1 \ \dots 1)$ , which never move chunks during the arrangement process. These exceptions correspond to the head and tail chunks. Lemma 2 gives the following theorem.

**Theorem 1.** The number l of representative elements is smaller than  $m = \lceil n/2b \rceil$  if  $m \ge 128$ .

**Proof**. Eq. (5) can be simplified further as follows.

$$l+2 = \frac{1}{M} \sum_{i=1}^{M} K^{\text{gcd}(i,M)} \leq \frac{1}{M} \sum_{i=1}^{M} K^{i}$$

(6)

$$= \frac{K(K^{M} - 1)}{M(K - 1)}$$

(7)

$$< \frac{K^{M+1}}{M(K-1)} \tag{8}$$

$M = \lceil \log 2m \rceil$ , K = 2 and  $x \leq \lceil x \rceil \leq x + 1$  for an arbitrary real number x, so we have

$$l < \frac{8m}{\log 2m} \tag{9}$$

$$\leq m, \text{ if } m \geq 128.$$

(10)

Eq. (10) indicates that 2m chunk indexes are reduced to at least half because a circular permutation comprises at least two elements (i.e., two chunk indexes). Therefore, the number l of representative elements is smaller than  $m = \lceil n/2b \rceil$ . Asymptotically, l is bounded by  $\mathcal{O}(n/\log n)$  from Eq. (9).

In addition, the proposed method generates  $O(n/\log n)$  thread blocks during chunk circulation because the method uses l thread blocks in total. The usage of registers per thread block (i.e., per circular permutation) is equivalent to the chunk size, where the chunk size is 4b in bytes if the signal data is stored in a 4-byte data type. Therefore, the proposed algorithm consumes  $O(n/\log n)$  registers if all of the thread blocks are processed simultaneously. However, due to the limited amount of computational resources, such as the shared memory and registers, CUDA restricts the maximum number of active thread blocks that can be processed simultaneously [18]. Therefore, our CUDA-based implementation runs with O(1) registers. Note that the proposed method achieves this restriction by data arrangement, which eliminates the data dependencies between different thread blocks. Such independent thread blocks are necessary to reduce the number of active thread blocks.

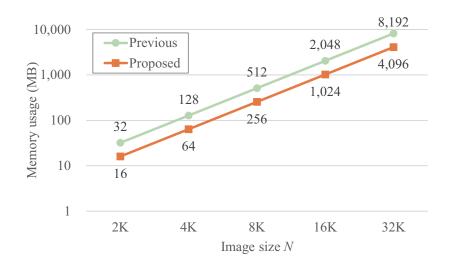

In summary, the proposed method consumes  $\lceil n/2b \rceil$  additional space locations

to perform the lifting-based DWT. Currently, we use b = 512, so this additional memory usage is an order of magnitude lower than the *n* needed by existing methods that distinguish the output buffer from the input buffer.

#### 4.4. Tiling-based Transformation

Tiling-based approaches [29, 30] are useful for dealing with large-scale data that exceeds the GPU memory capacity. These approaches split the data into tiles that are transformed separately. However, Eqs. (1) and (2) indicate that each element needs its neighbors to update its value. Consequently, separated transformation creates blocking artifacts at the tile boundaries, thereby excessive tiles can degrade the transformation quality.

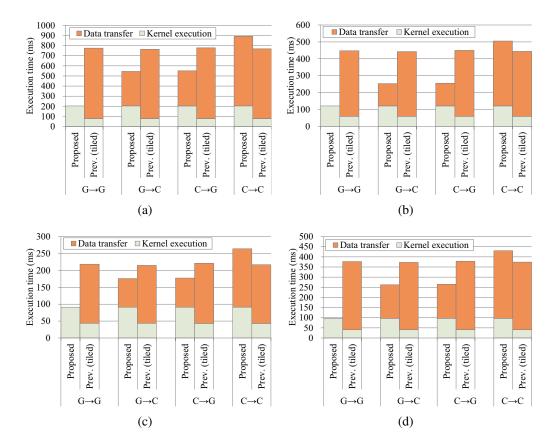

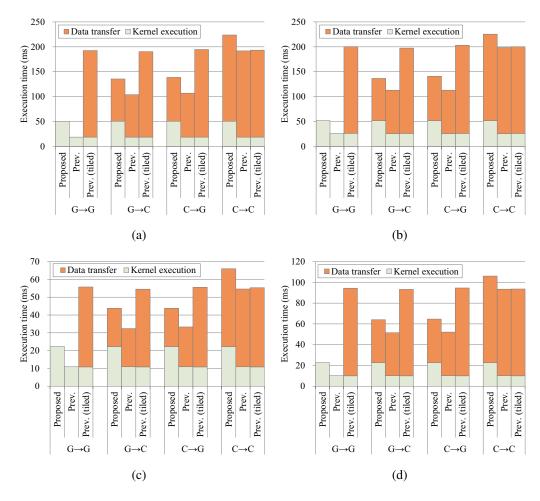

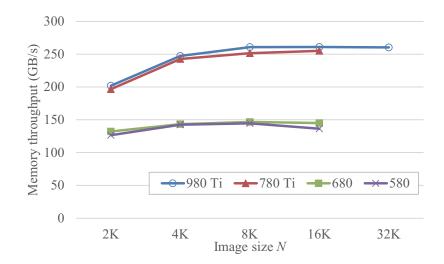

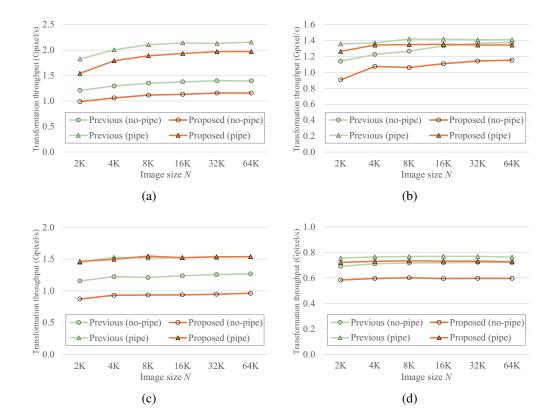

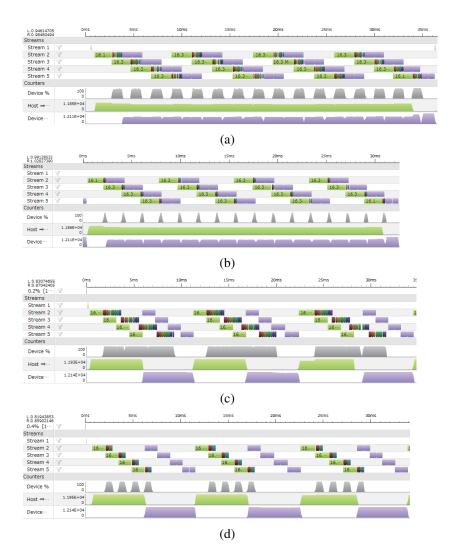

This degradation can be avoided by having halo regions for each tile (see Fig. 5); the input data is decomposed into small overlapping segments (with halo regions) to exactly transform all elements inside the tiles. Both the proposed and Laan's previous methods can be enhanced with a tiling-based approach by specifying a segment as the input. However, the proposed memory-saving method accepts roughly twice larger segments than those accepted by the previous method.